# Low Noise Chopper Multipath Amplifier with 129 dB Ripple Rejection using Floating High-Pass Filter and DC Servo Loop

<u>Yongsu Kwon<sup>1</sup></u>, Hyungseup Kim<sup>1</sup>, Donggeun You<sup>1</sup>, Hyunwoo Heo<sup>1</sup>, and Hyoungho Ko<sup>1,\*</sup>

<sup>1</sup>Department of Electronics Engineering, Chungnam National University, Daejeon 34134, Republic of Korea \*Corresponding Author (E-mail: <u>hhko@cnu.ac.kr</u>)

#### ABSTRACT

This paper presents a low noise chopper multipath amplifier using floating high-pass filter (HPF) and DC servo loop for microsensor interface circuits. Low noise characteristics are highly required in high performance sensor interface circuits. Reducing offsets and flicker noise by chopper stabilization technique is a common approach to gain low noise characteristics. The output ripple caused by the chopper up-modulation can be suppressed by a ripple reduction loop (RRL). However, the overall bandwidth is limited by implementing chopper stabilization technique. A multipath amplifier scheme is a solution for gaining wide bandwidth. The proposed chopper multipath amplifier scheme is implemented with a floating HPF and a DC servo loop (DSL) with passive low-pass filter (LPF) for fast common mode tracking and high ripple rejection. The RRL of the proposed scheme is implemented with floating HPF and a passive DSL without an additional amplifier. The multipath amplifier achieves offset rejection ratio of 129.32 dB by simulation results. The amplifier is fabricated using a 0.18  $\mu$ m complementary metal-oxide-semiconductor (CMOS) technology with and active area of 4.92 mm<sup>2</sup>. The measured input referred noise is 6.48 nV/ $\sqrt{Hz}$ , and the total current consumption is 117.2  $\mu$ A with a 1.8 V power supply.

#### INTRODUCTION

- With the growth of the sensor market, the demand for low-noise and highperformance readout circuits has increased. High-performance amplifiers with low noise and wide bandwidth are essential to satisfy these demands.

- A chopper-stabilization technique is adopted to reduce the 1/f noise and DC offset.

- To attenuate the output ripple caused by chopper up-modulation, a ripple reduction loop (RRL) is employed. However, there are disadvantages to generating notches of the transfer function in the chopping frequency band.

- To compensate for the notch characteristics in the chopping frequency band of the transfer function, a multipath architecture is employed.

- In this paper, a low noise chopper multipath amplifier using floating HPF and DC servo loop (DSL) for microsensor interface circuits is proposed. The RRL of the proposed scheme is implemented with floating HPF and a passive DSL without an additional amplifier.

## **CIRCUIT IMPLEMENTATION**

- Proposed low noise chopper multipath amplifier

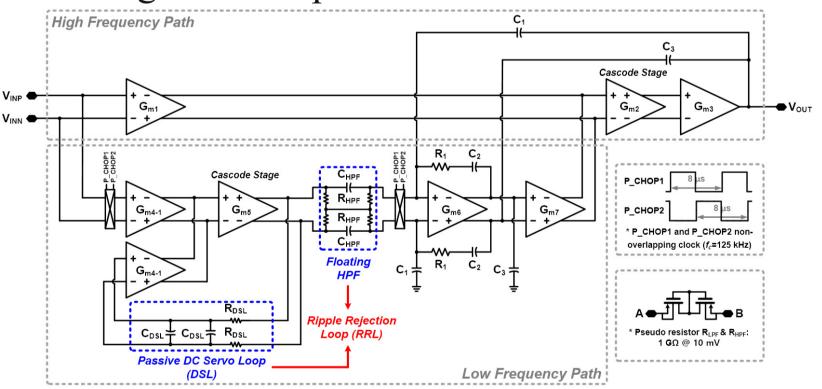

- Fig. 1 shows the schematic of proposed low noise chopper multipath amplifier.

- The multipath scheme consists with a high frequency path ( $G_{m1}$ ,  $G_{m2}$ , and  $G_{m3}$ ) and a low frequency path ( $G_{m4-1}$ ,  $G_{m4-2}$ ,  $G_{m5}$ ,  $G_{m6}$ , and  $G_{m7}$ ).

- The implemented passive DSL and floating HPF rejects the offset and ripple

### **EXPERIMENTAL RESULT**

- Die photograph and measurement environment

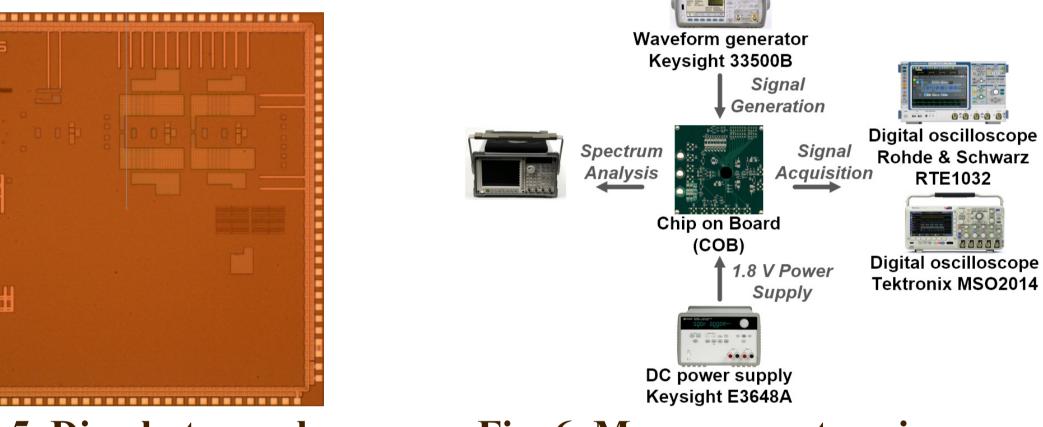

- Fig. 5 shows the die photograph of the low noise chopper multipath amplifier. The prototype chip is fabricated using a standard 0.18 μm CMOS process; the chip size is 4.92 mm<sup>2</sup>.

- Fig. 6 shows the measurement environment. The measured open loop gain is 132 dB with a unit gain bandwidth (UGBW) of 2.69 MHz. The total current consumption is 117.2 µA with a 1.8 V power supply and a chopper frequency of 125 kHz.

# Fig. 5. Die photograph

Fig. 6. Measurement environment

Input referred noise and common mode rejection ratio (CMRR)

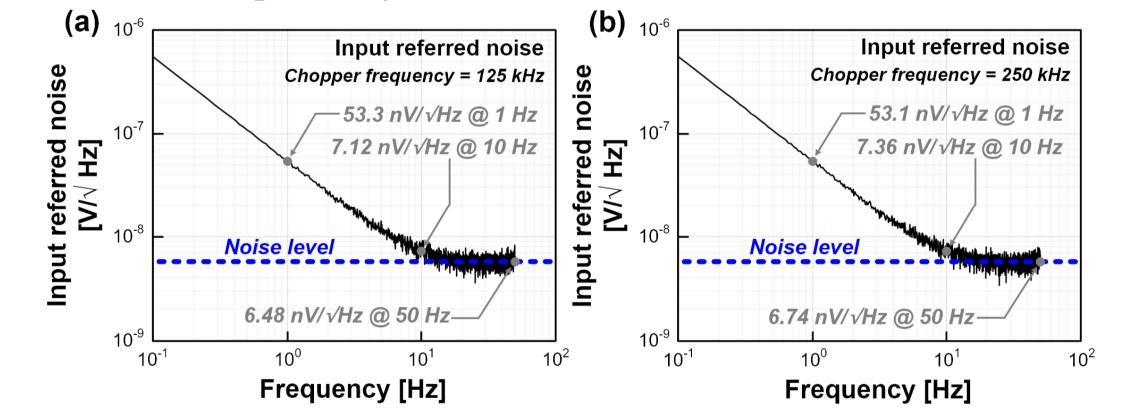

Fig. 7(a) and (b) show the measured input referred noise with chopper frequencies of 125 and 250 kHz, respectively.

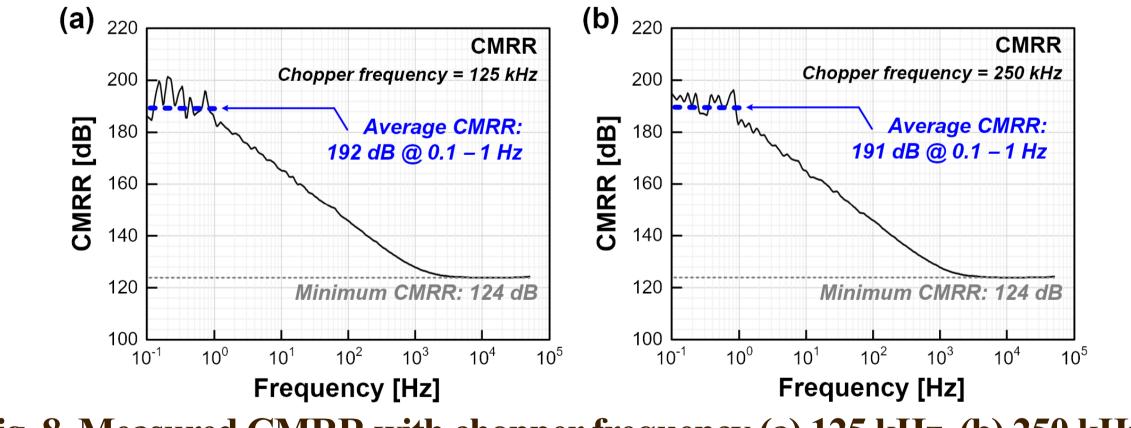

Fig. 8(a) and (b) show the measured CMRR at chopper frequencies of 125 and 250 kHz, respectively.

as a dual ripple rejection loop. The proposed RRL scheme has an advantage of high ripple rejection and low power consumption without an additional amplifier for an integrator compared to the conventional RRL schemes.

#### Fig. 1. Architecture of the proposed low noise chopper multipath amplifier

- Analysis of dual ripple rejection loops

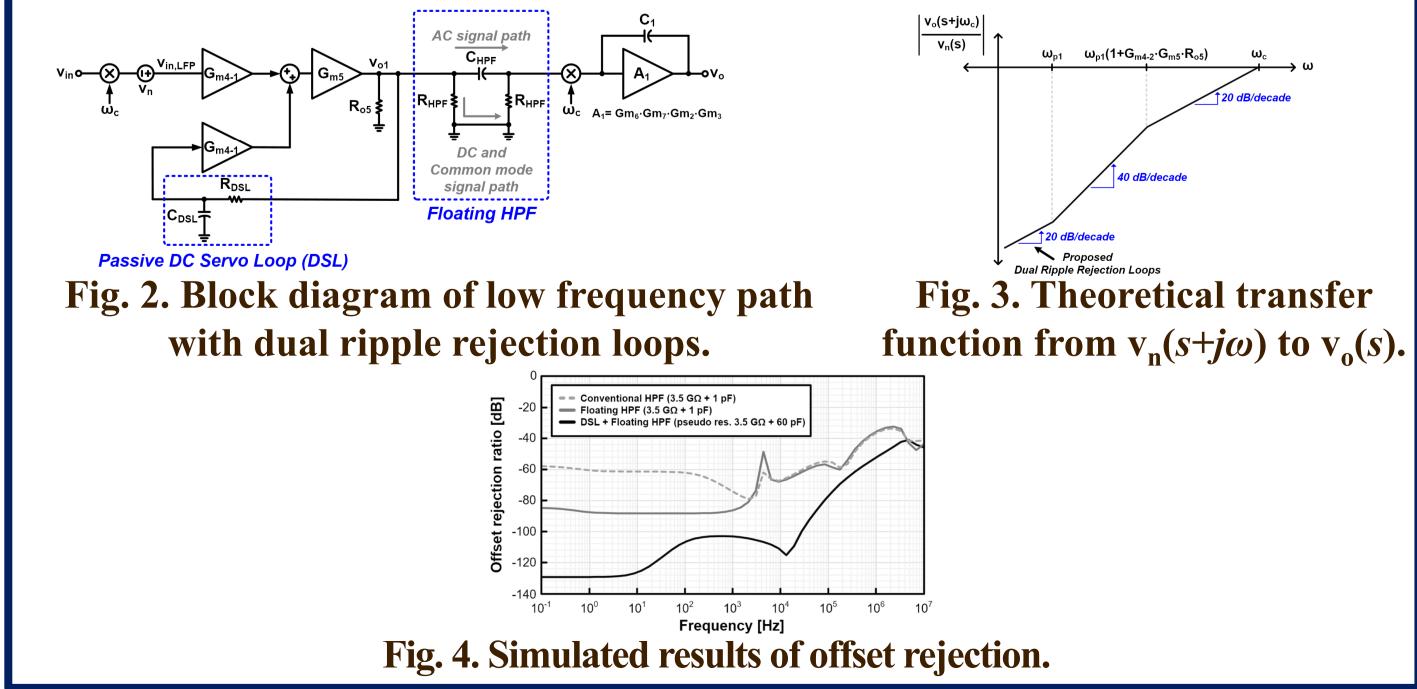

- Fig. 2 shows a block diagram of the low frequency path with the dual ripple rejection loops in the single-ended scheme. Assuming large  $A_1$ , the transfer function from  $v_n$  to  $v_o$  is given by:

$$\frac{v_o(s+j\omega_c)}{v_n(s)} = \frac{G_{m5}R_{o5}(1+s/\omega_{p1})}{s/\omega_{p1} + (1+G_{m4-2}G_{m5}R_{o5})} \cdot \frac{sC_{HPF}}{(s+j\omega_c)C_1}$$

- Fig. 3 shows the theoretical end-to-end transfer function from  $v_n$  to  $v_o$ . In the transfer function of the floating HPF, the zero is located at DC; thus, a high ripple rejection ratio at DC can be achieved.

- The performance comparisons of each scheme have been proceeded as shown in Fig. 4. At 0.01 Hz, the simulated offset rejections are 57.815 dB, 84.793 dB and 129.32 dB for each of conventional HPF, floating HPF and proposed DSL with floating HPF scheme.

Fig. 7. Input referred noise with chopper frequency (a) 125 kHz, (b) 250 kHz

Fig. 8. Measured CMRR with chopper frequency (a) 125 kHz, (b) 250 kHz

#### CONCLUSION

• A low noise chopper multipath amplifier using floating HPF and DC servo

- loop for microsensor interface circuits is presented.

- The RRL of the proposed scheme is implemented with floating HPF and a passive DSL without an additional amplifier.

- The multipath amplifier achieves offset rejection ratio of 129.32 dB by simulation results.

- The floating HPF achieves a fast common mode response and improved CMRR performance (of 192 dB) in the range of 0.1–1 Hz.

- The proposed multipath amplifier exhibits input noise and NEF performance of 6.48 nV/ $\sqrt{\text{Hz}}$  and 2.7, respectively, which are comparable to existing amplifiers.

#### ACKNOWLEDGEMENT

The chip fabrication and EDA tool were supported by the IC Design Education Center (IDEC), Korea.

CHUNGNAM NATIONAL UNIVERSITY Department of Electronics Engineering 99 Daehak-ro, Yuseong-gu, Daejeon 34134, Republic of Korea

INTEGRATED CIRCUIT DESIGN LABORATORY PHONE: +82-42-821-6285, EMAIL: hhko@cnu.ac.kr Department of Electronics Engineering, Chungnam National University